EDA Tool Usage for Verification Tasks

Synopsys VCS

Before working with VCS make sure that the product is properly installed and the LM_LICENSE_FILE or the SNPSLMD_LICENSE_FILE environment variables are pointing to the correct license servers.

Also make sure that the path containing all the executables is added to the PATH variable as well.

The main executable of concern is 'vcs'. All compilations are to be done using this executable.

Compiling basic Verilog and System Verilog Files.

For the sake of simplicity we will use a very simple RTL file of a 4 bit counter for all compilation examples here. The content of the file is shown below :

The name of the file is 'counter_4bit.v'

Let us now create a small verilog TB for the above code. This TB instantiates the counter and drives input vectors to it. Refer the TB code below :

The above verilog test bench along with the counter design can be compiled with the below command :

The above command compiles the codes and produces and executable called 'simv' in the same directory. This executable can be invoked to run the code.

Alternatively the -R switch can also be specifed at the time of compiling to run the executable after the compilation successfully finishes. This omits the need to having to run the executable manually.

Command shown below :

The command produces the below output :

The prints specified in the Counter TB can be seen in the log dump.

Additionally the -l switch can also be specified to dump all the output to a log file. Refer below command in which we dump all the logs to a sim.log file. The log file can be any name specified by the user.

Dumping VCD (Value Change Dump) File for the Simulation

A VCD file can be dumped for the code for dumping and viewing the waveforms in VCD format.

VCD is a very old and crude format for representing waveforms. Many tools support it for backward compatibility. Refer below command fro dumping a VCD file. The command will create a VCD file 'dump.vcd' in the same directory.

Dumping VPD for DVE (Discovery Visual Environment)

DVE is the GUI environment for Synopsys VCS. It is the default tool for opening and working with dump waveform files. DVE recognizes .vcd and .vpd files as standard input files that can be opened for waveform analysis.

To dump a .vpd wave file, add the below code to your top file.

And then compile their code.

After the compile and run is complete, this creates the file 'wave_dump.vpd' in the same directory. The dve gui environment can then be invoked by using the below command line.

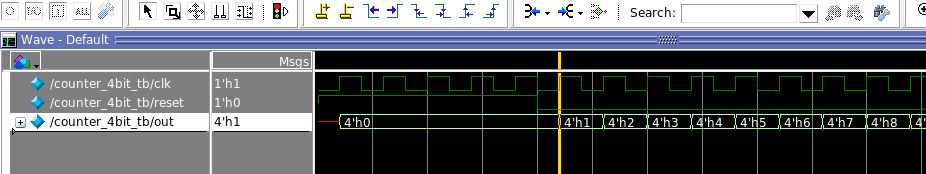

As can be seen in below figure, the compilation completed successfully and a vpd dump was created with the expected waveform behavior.

Dumping FSDB for Verdi

Verdi is a very popular and widely accepted GUI platform from synopsys for that is used for a variety of verification related purposes like :- Waveform Debug

- Code back trace

- Interactive Debugging

- Coverage Analysis

- Verification Planning using HVP Annotation and Spec Annotation

Verdi takes the .fsdb file format as input for waveform debug. Thus an FSDB dump has to be generated for this purpose.

To dump FSDB file, User needs to call the $fsdbDumpvars() function in their top hierarchy. The code snippet to add is shown below :

User needs to add the switches -lca -kdb -debug_access+all to the vcs command at the time of compiling.

Thus the equivalent command to dump FSDB file for the above counter TB example becomes :

This creates the specified fsdb file 'my_wave_dump.fsdb' in the same directory. The FSDB file can be invoked to be opened in the Verdi GUI window using the below command :

- -full64 : Compiles in 64 bit mode for 64 bit simulations.

- -V : Verbose mode. Print VCS version and extended summary information. Prints VCS compile and run-time version numbers, and copyright information, at start of simulation.

- -sverilog : Enables the etensions to the Verilog language in the Accellera SystemVerilog specification.

- +incdir+< directory path to include > : Add directories to include, to pick for files that are specified as part of the `include directive.

- -define=< define name >: Specifying compile time defines without values. For example : -define=MY_DEFINE.

- -define=< define name >=< define value > : Specifying compile time defines with values. -define=MY_DEFINE=10.

- +< Runtime Plusarg > : For example : '+MY_PLUSARG'

- +< Runtime Plusarg >=< Runtime Plusarg value> : For example : '+MY_PLUSARG=123'

Cadence NC-Sim

Another popular verification and RTL simulation tool is NC-Sim from Cadence Design Systems.

The main executable of concern is 'irun / xrun' and 'ncverilog'. All compilations are to be done using this executable. Also make sure that the path containing all the executables is added to the PATH variable as well.

We will pick the same Counter TB example here as well.

The proprietary waveform dump format used by cadence simulators is .trn which is created under a .shm database, thus a .trn file has to be dumped for your code.

We will consider compiling with xrun here.

Similar to how we added some logical code to the top module when we dumped vpd and fsdb formats. In the same way add below logic to your top TB file for calling compiler tasks to dump .shm database files.

The code is compiles using 'xrun' using the below command :

Just like before, the -l switch here is used to dump all output to a specified file name. (Here its taken as sim.log).

The command produces the below output :

The above command will create a directory 'my_wave_dump.shm' in the current directory, which will contain the files my_wave_dump.dsn and my_wave_dump.trn. The '.trn' is our dump file of interest.

The GUI debug tool of Cadence Design Systems for working with '.trn' files is simvision.

Use below command for opening the .trn file with simvision.

The GUI window opens and we can add our signals and can see the behavior as expected.

- +sv : Specified when trying to simulate System Verilog files.

- -access : The -access option is passed to the elaborator to provide read access to simulation objects (Valid values are +r , +w or +rw).

- -c or -elaborate: Parse/compile the source files, elaborate the design, and generate a simulation snapshot, but do not simulate..

- -name < snapshot name > : When compiled with the -c or the -elaborate option for compile only, the -name options lets the user specify a 'snapshot_name'. This name has to be specified to the -r oprtion as argument when trying to run a simulation for that build.

- -r < snapshot name > : Simulate the last snapshot generated by an xrun command. The -R option lets you simulate the same snapshot multiple times using different simulator command-line options or Tcl command input files. You can prebuild a snapshot (by using the -c or -elaborate option) and then use the -R option to simulate that snapshot multiple times.

- +define+< define name >: Specifying compile time defines without values. For example : +define+MY_DEFINE.

- +define+< define name >=< define value > : Specifying compile time defines with values. +define+MY_DEFINE=10.

- +< Runtime Plusarg > : For example : '+MY_PLUSARG'

- +< Runtime Plusarg >=< Runtime Plusarg value> : For example : '+MY_PLUSARG=123'

Mentor Graphics / Siemens - Questasim

The next most popular tool for Functional Simulations is Questasim / Modelsim from Mentor Graphics ( Now Siemens ).

The main executable for compiling code database is vlog, and the simulation runner and GUI in use is vsim. make sure that the path containing all the executables is added to the PATH variable.

The proprietary waveform dump format used by the Questa simulator is .wlf. Thus in this example we will try creating a .wlf waveform dump for out counter example.

We will pick the same Counter TB example here as well.

Similar to how we basically added some simulator specific routines to a procedural block earlier, we will follow a similar drill here as well. Just add below code to your top code.

The counter code is compiled using vlog. Command used to compile is given below :

A detailed list of all arguments supported for 'vlog' with its usage can be obtained using -help. Command : vlog -help

Once the code is compiled. It can be now be simulated using vsim. vsim takes simulator commands to run and finish the simulation. Thus commands 'run all' and 'quit' have to be specified to it. This can be done explicitly through the -do argument for 'vsim' or both the commands can be saved to a .do file, and the file can be specified as input to the vsim command.

We will explore both the approaches here.

Command Example 1 : In below command the 'run all' command is specified to the -do argument. This invokes the simulator in batch mode and runs the simulation.

Command Example 2 : In this example, both the commands i.e. 'run -all' and 'quit' are save to a .do file 'command.do' (Name arbitrarily chosen).

The contents of the command.do file is shown below :

This file can now be specified as input to the 'vsim' command. Example command below :

NOTE : Both the example commands are equivalent and produce the same result.

After running the simulation the below output is produced :

The specified .wlf can be seen to be generated in the same directory. User can open the .wlf waveform dump using the below command :

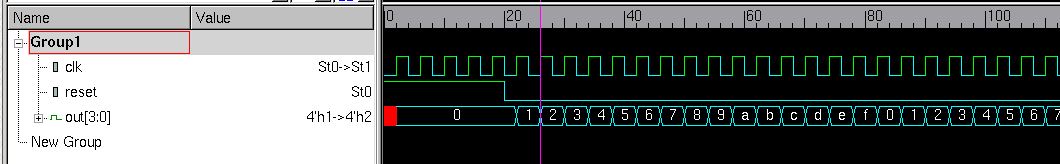

In the opened GUI window, after adding the respective signals, we can see that the dump is as expected (shown below).