Logic Strength Modelling

Logic Strength Modelling

The Verilog HDL provides for accurate modeling of signal contention, bidirectional pass gates, resistive MOS devices, dynamic MOS, charge sharing, and other technology-dependent network configurations by allowing scalar net signal values to have a full range of unknown values and different levels of strength or combinations of levels of strength.

This multiple-level logic strength modeling resolves combinations of signals into known or unknown values to represent the behavior of hardware with improved accuracy.

A strength specification has two components :- The strength of the 0 portion of the net value, called strength0, which is designated by one of the following : supply0, strong0, pull0, weak0 and highz0.

- The strength of the 1 portion of the net value, called strength1, which is designated by one of the following : supply1, strong1, pull1, weak1 and highz1.

There are 4 Driving Strengths : supply, strong, pull and weak

There are 3 Storage Strengths : large, medium and small

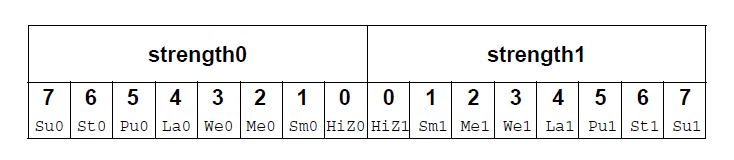

Table below demonstrates the continuum of strengths. The left column lists the keywords used in specifying strengths. The right column gives correlated strength levels.

| Strength Name | Strength Level |

|---|---|

| supply0 | 7 |

| strong0 | 6 |

| pull0 | 5 |

| large0 | 4 |

| weak0 | 3 |

| medium0 | 2 |

| small0 | 1 |

| highz0 | 0 |

| highz1 | 0 |

| small1 | 1 |

| medium1 | 2 |

| weak1 | 3 |

| large1 | 4 |

| pull1 | 5 |

| strong1 | 6 |

| supply1 | 7 |

It is possible to think of the strength of signals as locations on the scale below :

- If the signal value of a net is known, all of its strength levels shall be in either the strength0 part of the scale or all strength levels shall be in its strength1 part.

- If the signal value of a net is unknown (X), it shall have strength levels in both the strength0 and the strength1 parts.

- A net with a signal value Z shall have a strength level only in one of the 0 subdivisions of the parts of the scale.